Chapter 10

Analog Integrated Circuits

In earlier chapters of this text the low-frequency behavior of differential pairs, current mirrors, output buffers, and other circuit building blocks was investigated using Spice. These were also combined, in a rather simplistic way, to form an operational amplifier whose large and small-signal static behavior was analyzed using Spice. This same approach is also used to realize other more sophisticated analog ICs. The very-popular bipolar 741 op amp circuit used in several of the examples of Chapter 2 is one such example. In this chapter we shall perform a detailed analysis of the 741 op amp using Spice. This will include an investigation into both its static and dynamic circuit behavior. We will also take a brief look at the expected thermal noise behavior of this op amp using the noise analysis capabilities of Spice. Following this, we shall investigate several CMOS and BiCMOS op amp designs that are finding important application in VLSI systems. Finally, we shall investigate the behavior of a D/A and an A/D converter circuits.

10.1 A Detailed Analysis Of The 741 Op Amp Circuit

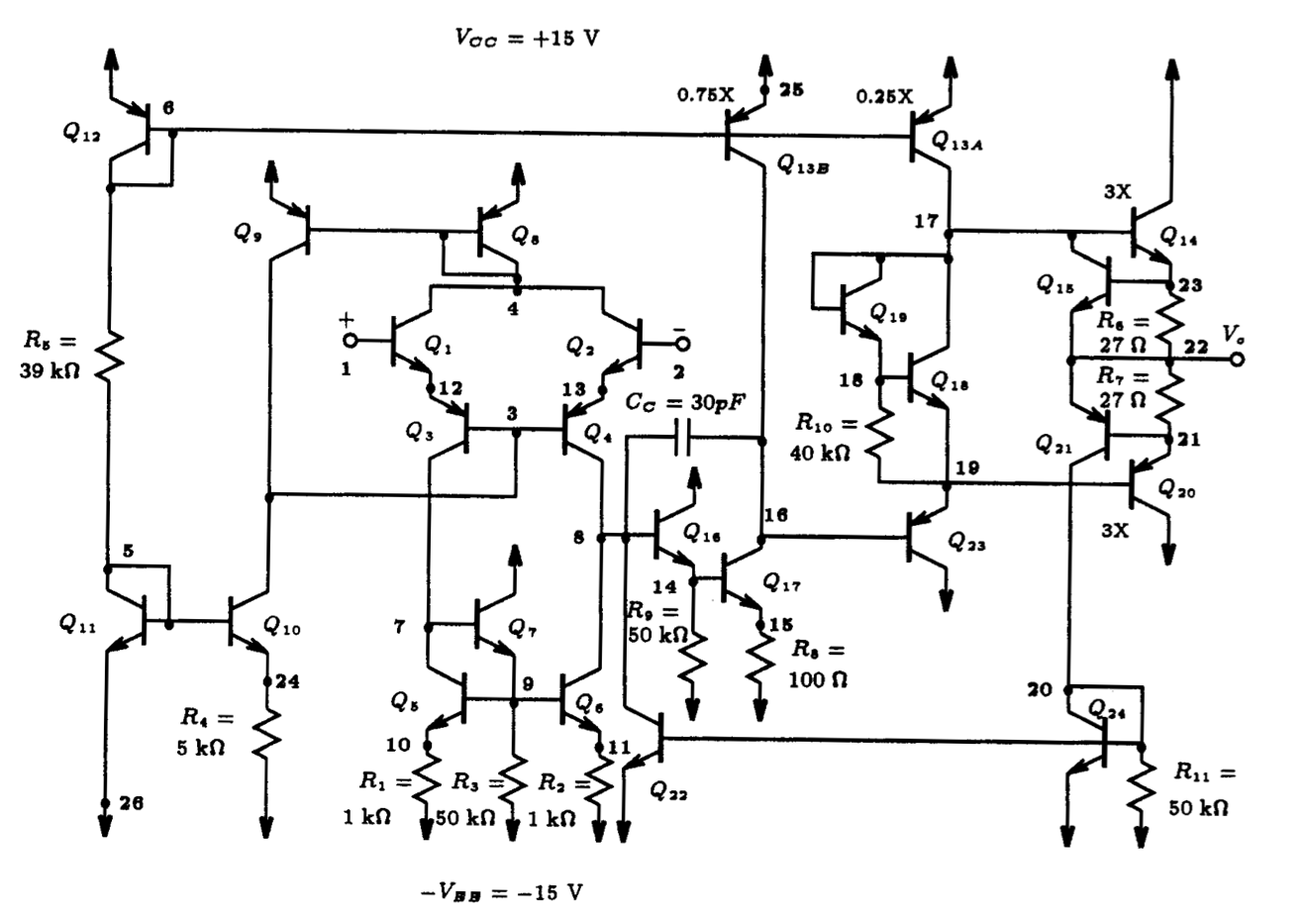

A detailed circuit schematic of the 741 op amp is shown in Fig. 10.1. It consists of five main parts: (i) bias circuit, (ii) the input gain stage, (iii) the second gain stage, (iv) the output buffer, and (v) the short-circuit protection circuit. Each one of these stages, in one form or another, was briefly discussed and analyzed with Spice in previous chapters of this text. For a detailed explanation of each section of the 741 op amp, see the discussion in Chapter 10 of Sedra and Smith, 3rd Edition.

In the following we shall demonstrate how one can utilize Spice to analyze the behavior of a complex analog circuit, such as the 741 op amp circuit shown in Fig. 10.1. Many of the procedures and set-ups used here would have been seen by our readers in early examples of this text, so our emphasis here serves more as a review of these methods; albeit, in a more complex setting. One exception to this is the Spice method used to compute the thermal noise behavior of the 741 op amp.

Assuming the typical set of device parameters for both the npn and pnp transistors shown in Table 10.1, we shall proceed to compute the DC operating point of the amplifier, its gain and frequency response, slew-rate and noise behavior. A reduced version of these parameters were used by Sedra and Smith in their hand analysis of the 741 op amp circuit in Chapter 10 of their text. Direct comparisons can be made between the results obtained through hand analysis and those obtained with Spice.

The Spice input file describing the circuit of the 741 op amp is listed in Fig. 10.2. The differential input is driven by the familiar multiple-input voltage-source arrangement discussed in section 6.1 and shown again in Fig. 10.3. This multiple source arrangement provides maximum flexibility when it comes to performing different types of analysis (e.g., differential-mode and common-mode transfer characteristics) on a differential amplifier.

|

Fig. 10.1: The 741 Op Amp Circuit.

|

The 741 Op-Amp

** Circuit Description **

* power supplies Vcc 25 0 DC +15V Vee 26 0 DC -15V

* differential-mode signal level Vd 101 0 DC 0V Rd 101 0 1 EV+ 1 100 101 0 +0.5 EV- 2 100 101 0 -0.5 * common-mode signal level Vcm 100 0 DC 0V

* 1st or input stage Q1 4 1 12 npn Q2 4 2 13 npn Q3 7 3 12 pnp Q4 8 3 13 pnp Q5 7 9 10 npn Q6 8 9 11 npn Q7 25 7 9 npn Q8 4 4 25 pnp Q9 3 4 25 pnp R1 10 26 1k R2 11 26 1k R3 9 26 50k

* 2nd stage Q13B 16 6 25 pnp 0.75 Q16 25 8 14 npn Q17 16 14 15 npn R8 15 26 100 R9 14 26 50k Cc 8 16 30p

* output or buffer stage Q13A 17 6 25 pnp 0.25 Q14 25 17 23 npn 3 Q18 17 18 19 npn Q19 17 17 18 npn Q20 26 19 21 pnp 3 Q23 26 16 19 pnp R6 22 23 27 R7 21 22 27 R10 18 19 40k

* short-circuit protection circuitry Q15 17 23 22 npn Q21 20 21 22 pnp Q22 8 20 26 npn Q24 20 20 26 npn R11 20 26 50k

* biasing stage Q10 3 5 24 npn Q11 5 5 26 npn Q12 6 6 25 pnp R4 24 26 5k R5 6 5 39k

* transistor model statements .model npn NPN ( Bf=200 Br=2.0 VAf=125V Is=10fA Tf=0.35ns + Rb=200 Rc=200 Re=2 Cje=1.0pF Vje=0.70V Mje=0.33 Cjc=0.3pF + Vjc=0.55V Mjc=0.5 Cjs=3.0pF Vjs=0.52V Mjs=0.5)

.model pnp PNP ( Bf=50 Br=4.0 VAf=50V Is=10fA Tf=30ns + Rb=300 Rc=100 Re=10 Cje=0.3pF Vje=0.55V Mje=0.5 Cjc=1.0pF + Vjc=0.55V Mjc=0.5 Cjs=3.0pF Vjs=0.52V Mjs=0.5)

** Analysis Requests ** .OP .DC Vd -400uV -200uV 10uV

** Output Requests ** .PLOT DC V(22) .probe .end

Fig. 10.2: The Spice input deck for analyzing the DC circuit behavior of the 741 op amp. Since the number of transistors exceed the limit imposed by the student version of PSpice, this particular Spice input deck is to be processed by the professional version of PSpice which has no transistor count limit.

|

|

Table 10.1: Typical Spice parameters for integrated npn and pnp transistors [Gray and Meyer, 1984]. |

Fig. 10.3: The multiple input voltage source used to drive the differential input of the 741 op amp.

|

|

|

|

DC Analysis of the 741

The first analysis that we will request that Spice perform is a DC operating point analysis. This will provide us with some insight into the DC behavior of all the transistors in the op amp circuit for grounded inputs - in case it's needed. In addition to this, we shall also request a DC sweep of the input differential voltage. This will indicate the boundaries of the high-gain region of the amplifier so that other analysis can be performed on the amplifier while it's biased around a known operating point; preferably a point within the linear region of the amplifier. Initially we set-up the DC sweep so that the input differential voltage is varied between the limits of the two power supplies. However, after the first submission to Spice, we refined the sweep range to vary between -400 uV and -200 uV in 10 uV increments so that we would obtain better resolution around the high-gain region of the amplifier[1]. During this analysis the input common-mode level is held at ground potential.

On completion of Spice, the large-signal differential-mode transfer characteristics of the 741 op amp, together with its DC operating point information, are calculated. The former is on display in Fig. 10.4. From this graph we observe several characteristics of the op amp. The first is that the linear region of the amplifier, as seen from the input terminals of the op amp, is bounded between -360 uV and -268 uV. Conversely, this corresponds to a maximum output voltage swing bounded in the negative direction by -13.2 V, and +13.2 V in the positive direction. This suggests that the small-signal DC gain of this amplifier is approximately 13.2-(-13.2) / -268u -(-360u )=+287 kV/V. We also notice that the transfer characteristics of this amplifier cross the 0 V output axis somewhere between -320 uV and -310 uV. A careful look using the Probe capability of PSpice indicates that the cross-over point occurs at -314.1 uV. Thus, this particular amplifier has an input-referred DC offset voltage of +314.1 uV. This is the systematic offset of the op amp design and does not include offsets that result from component mismatches.

Reviewing the DC operating point information (which is not shown here) reveals that for grounded amplifier inputs, transistors Q13A and Q13B are saturated, causing transistors Q14, Q18-Q20, and Q23 to cutoff. Except for these and the transistors of the protection circuit, the remaining transistors are operating in their active regions. Other DC information, such as input bias currents, static power dissipation, etc., was calculated through the .OP command; however, these results are obtained when the op amp is biased outside of its normal operating region i.e., linear region. Since the op amp is generally operated in its linear region, it is more appropriate to repeat the DC operating point command with the op amp is biased in its linear region. This is easily accomplished by applying a differential input offset voltage of -314.1 uV across the two inputs to the op amp. We can then repeat the DC analysis with the following element statement replacing the one listed in Fig. 10.2:

Vd 101 0 DC -314.1uV.

On completion of Spice, we obtain the following small-signal bias solution:

|

**** SMALL SIGNAL BIAS SOLUTION TEMPERATURE = 27.000 DEG C ******************************************************************************

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1)-157.1E-06 ( 2) 157.1E-06 ( 3) -1.0496 ( 4) 14.4540 ( 5) -14.3510 ( 6) 14.3420 ( 7) -13.9310 ( 8) -13.7450 ( 9) -14.4640 ( 10) -14.9920 ( 11) -14.9920 ( 12) -.5265 ( 13) -.5263 ( 14) -14.2900 ( 15) -14.9340 ( 16) -1.1909 ( 17) .5834 ( 18) .0348 ( 19) -.5789 ( 20) -15.0000 ( 21) -.0040 ( 22) 592.6E-06 ( 23) .0052 ( 24) -14.9020 ( 25) 15.0000 ( 26) -15.0000 ( 100) 0.0000 ( 101)-314.1E-06

VOLTAGE SOURCE CURRENTS NAME CURRENT

Vcc -1.841E-03 Vee 1.841E-03 Vd 3.141E-04 Vcm -6.897E-08

TOTAL POWER DISSIPATION 5.52E-02 WATTS

**** VOLTAGE-CONTROLLED VOLTAGE SOURCES

NAME EV+ EV- V-SOURCE -1.571E-04 1.571E-04 I-SOURCE -3.440E-08 -3.456E-08

|

From the above, we see that the 741 op amp dissipates a static power of 55.2 mW. We can also calculate the input bias and offset currents of the op amp from the currents passing through the two VCVS, EV+ and EV-. The input bias current IB is (-34.40n) + (-34.56n) / 2 =34.48 nA and the offset current IOS is |(-34.40n) - (-34.56n)| = 0.16 nA. This particular offset current is due solely to the systematic offset of the op amp design itself, as opposed to any random offset effect that can occur during manufacture.

Also included in the Spice output file is a detailed listing of the operating point of each transistor. Rather than list all of this information here, instead, in Table 10.2 we list the collector current (in uA) of each transistor found in the 741 op amp circuit. These are also compared with the current levels computed using hand analysis by Sedra and Smith. As is self-evident, there is reasonable agreement between the two sets of results.

To determine the input common-mode range (CMR) of the 741 op amp, we shall sweep the input common-mode level VCM between the two power supply limits. To ensure that the op amp is biased in the linear region, we maintain the input differential offset voltage at -314.1 uV. To accomplish our task of varying the input common-mode level, we simply alter the .DC sweep command listed in the Spice deck of Fig. 10.2 according to:

.DC Vcm -15V +15V 0.1V.

No other alterations are necessary.

|

Table 10.2: DC collector currents of the 741 circuit in uA as computed by hand analysis and by Spice. |

|

Fig. 10.4: The large-signal differential input transfer characteristics for the 741 op amp circuit. The input common-mode voltage level is set to zero volts.

|

Fig. 10.5: The large-signal common-mode DC transfer characteristics of the 741 op amp circuit shown in Fig. 10.1. An input differential offset voltage of -314.1 uV is applied to the input of the amplifier input to prevent any premature saturation. |

Re-submitting the revised input file to Spice results in the large-signal common-mode DC transfer characteristic displayed in Fig. 10.5. Here we see that linear operation is maintained over an input common-mode range (CMR) between -10.0 V and +8.05 V corresponding to an output voltage swing varying between -13.26 V and 14.27 V. The lower limit of the CMR is caused by Q13A of the second stage saturating. Similarly, the upper limit of the CMR is caused by transistor Q17 also of the second stage saturating. We can also estimate the common-mode voltage gain in the linear region of the op amp to be (-13.26)- 14.27 / 8.05-(-10.0) =-1.53 V/V.

We should note that these results are quite different from those normally encountered in an actual 741 op amp. Typically, the input CMR is determined by the transistors of the front-end stage leaving their linear regions rather than transistors of the second stage - as we have seen above. We attribute this difference to the fact that the 741 op amp consists of 6 different types of transistors (i.e., small npn, large npn, lateral pnp, substrate pnp, dual-emitter pnp and a dual-collector pnp) each having different terminal characteristics. On the other hand, the above Spice simulation of the 741 op amp models the diversity of the different transistors with only two model types. Thus, some behavior of the actual 741 op amp is not properly captured in our simulations.

The above results are all examples of a large-signal analysis. Much of the analysis performed by Sedra and Smith is based on small-signal analysis. To obtain the small-signal parameters of the op amp we make use of the .TF command of Spice. For instance, the small-signal differential voltage gain and small-signal output resistance of the op amp can be computed by adding the following command to the Spice deck shown listed in Fig. 10.2:

.TF V(22) Vd

It is important to maintain the input differential offset voltage at -314.1 uV in order to keep the amplifier in its linear region. The input common-mode level is also held at ground potential. The results of Spice are listed below:

|

**** SMALL-SIGNAL CHARACTERISTICS

V(22)/Vd = 2.946E+05

INPUT RESISTANCE AT Vd = 1.000E+00

OUTPUT RESISTANCE AT V(22) = 1.064E+02

|

Here we see that the small-signal differential voltage gain of +294.6 kV/V is quite close to the value +287 kV/V estimated from the slope of the op amp large-signal transfer characteristics shown in Fig. 10.4. The input resistance stated here is not the input differential resistance of the op amp. Rather, this is the 1 W resistance connected directly to Vd. To obtain an estimate of the input resistance of the op amp, we shall instead use the results of the AC analysis presented below. The output resistance of the op amp is seen to be quite low at 106.4 W.

We can repeat the above .TF analysis with respect to the input common-mode level around the operating point defined by VCM=0 V and Vd=-314.1 uV. One simply utilizes the command:

.TF V(22) Vcm

The results of the analysis are then found in the Spice output file as follows:

|

**** SMALL-SIGNAL CHARACTERISTICS

V(22)/Vcm = -1.555E+00

INPUT RESISTANCE AT Vcm = 6.064E+08

OUTPUT RESISTANCE AT V(22) = 1.064E+02

|

The common-mode voltage gain is -1.555 V/V, the input common-mode resistance is seen to be a very large 606.4 MW, and the output resistance is, as expected, the same as the previous calculation of 106.4 W.

Dividing the differential voltage gain of 2.946 x 105 V/V by the magnitude of common-mode voltage gain of 1.555 V/V we obtain the common-mode rejection ratio (CMRR) for the 741 op amp to be 105.6 dB.

We can carry the small-signal analysis over to the frequency domain and have Spice compute the differential magnitude and phase response of the op amp. Several alterations must be made to the Spice input file shown listed in Fig. 10.2. For starters, the input differential excitation should be changed to include an AC voltage component. A one-volt AC signal will be applied. The amplitude of this AC input is not important because an AC analysis is performed using a linearized model of the transistor circuit. A 1-volt amplitude is commonly chosen for the input signal because, in this way, the output voltage directly represents the transfer function of the circuit. We maintain the input DC offset voltage at -314.1 uV in order to maintain the op amp in its linear region. Thus, the input excitation statement should be changed to read as follows:

Vd 101 0 DC -314.1uV AC 1V.

Gain and Frequency Response of the 741

Following this, we shall request that Spice compute the frequency response of the amplifier over a frequency interval beginning at 0.1 Hz and ending at 100 MHz using the following statement:

.AC DEC 10 0.1Hz 100MegHz

A plot statement can be included in the input file to graphically display the output voltage results of the frequency response analysis. Its syntax would appear as follows:

.PLOT AC VdB(22) Vp(22).

We shall also include a .PRINT statement for the magnitude of the small-signal current flowing through the two VCVSs in series with the op amp input terminals. This will allow us to calculate the input differential resistance of the op amp knowing that the small-signal input differential voltage applied to the amplifier is 1 V. The command line for this is

.PRINT AC Im(EV+) Im(EV-).

The revised Spice input file for calculating the small-signal frequency response of the 741 op amp is listed in Fig. 10.6.

The results of the frequency-domain analysis are shown in Fig. 10.7. The low-frequency behavior is dominated by a single-pole response having a low-frequency gain of 109.4 dB and a 3-dB bandwidth of approximately 2.6 Hz. The unity-gain frequency ft is read directly off the graph using Probe to be 0.652 MHz. We also find that this amplifier has a phase margin of 66.7°. The presence of a second pole is also evident. It is located at approximately 1.82 MHz.

The low frequency current drawn by the op amp input terminals was found by Spice to be as follows:

|

FREQ IM(EV+) IM(EV-) 1.000E-01 2.766E-07 2.732E-07 |

We see here that there is a small difference between the two currents drawn by the op amp input terminals. This difference is due to op amp systematic offset. To determine the input differential resistance to the amplifier under such asymmetric conditions, we shall work with the average of the two base currents. In this way, we can eliminate the presence of the offset current in the resistance calculation. Thus, we compute the average input base current to be 274.9 nA and therefore obtain the input differential resistance at 3.64 MW.

|

The 741 Op-Amp

** Circuit Description **

* power supplies Vcc 25 0 DC +15V Vee 26 0 DC -15V

* differential-mode signal level Vd 101 0 DC -314.1uV AC 1V Rd 101 0 1 EV+ 1 100 101 0 +0.5 EV- 2 100 101 0 -0.5 * common-mode signal level Vcm 100 0 DC 0V

* 1st or input stage Q1 4 1 12 npn Q2 4 2 13 npn Q3 7 3 12 pnp Q4 8 3 13 pnp Q5 7 9 10 npn Q6 8 9 11 npn Q7 25 7 9 npn Q8 4 4 25 pnp Q9 3 4 25 pnp R1 10 26 1k R2 11 26 1k R3 9 26 50k

* 2nd stage Q13B 16 6 25 pnp 0.75 Q16 25 8 14 npn Q17 16 14 15 npn R8 15 26 100 R9 14 26 50k Cc 8 16 30p

* output or buffer stage Q13A 17 6 25 pnp 0.25 Q14 25 17 23 npn 3 Q18 17 18 19 npn Q19 17 17 18 npn Q20 26 19 21 pnp 3 Q23 26 16 19 pnp R6 22 23 27 R7 21 22 27 R10 18 19 40k

* short-circuit protection circuitry Q15 17 23 22 npn Q21 20 21 22 pnp Q22 8 20 26 npn Q24 20 20 26 npn R11 20 26 50k

* biasing stage Q10 3 5 24 npn Q11 5 5 26 npn Q12 6 6 25 pnp R4 24 26 5k R5 6 5 39k

* transistor model statements .model npn NPN ( Bf=200 Br=2.0 VAf=125V Is=10fA Tf=0.35ns + Rb=200 Rc=200 Re=2 Cje=1.0pF Vje=0.70V Mje=0.33 Cjc=0.3pF + Vjc=0.55V Mjc=0.5 Cjs=3.0pF Vjs=0.52V Mjs=0.5)

.model pnp PNP ( Bf=50 Br=4.0 VAf=50V Is=10fA Tf=30ns + Rb=300 Rc=100 Re=10 Cje=0.3pF Vje=0.55V Mje=0.5 Cjc=1.0pF + Vjc=0.55V Mjc=0.5 Cjs=3.0pF Vjs=0.52V Mjs=0.5)

** Analysis Requests ** .AC DEC 10 0.1Hz 100MegHz

** Output Requests ** .PLOT AC Vdb(22) Vp(22) .PRINT AC Im(EV+) Im(EV-) .probe .end

Fig. 10.6: The Spice input deck for computing the frequency response of the 741 op amp. |

Fig. 10.7: The differential magnitude and phase response of the 741 op amp. The low frequency response behavior of the 741 op amp is dominated by a single-pole roll-off beginning at 2.6 Hz. A second pole is also evident at 1.82 MHz. |

Slew-Rate Limiting of the 741

An important attribute of op amp behavior that usually limits the high-frequency operation of op amp circuits is its slew-rate limiting. Connecting the op amp in a unity-gain configuration and applying a large voltage pulse to its input will reveal both the positive-going and negative-going slew-rate of this op amp, as demonstrated in Fig. 10.8. The Spice input file depicting this arrangement is provided in Fig. 10.9. Here a zero-valued voltage source described by

Vshort 2 22 0

is used to form a direct connection between the op amp output and its negative input terminal. This avoids having to renumber the negative input terminal of the op amp in the Spice deck with the same number used to describe the op amp output. Another voltage source is used to create the input pulse:

Vd 1 0 PWL ( 0,-5V 1ns,+5V 30000ns,+5V 30001ns,-5V 1s,-5V ).

Notice that this input pulse signal is described in a piece-wise linear fashion, beginning at a low level of -5 V and quickly rising to +5 V one ns after this, staying there for 30 us and then returning to the -5 V level one ns later. It remains at this low level of -5 V for the rest of the duration of the pulse. A transient analysis is requested to compute the response of the op amp circuit arrangement over a 100 us interval using a 0.1 ns sampling interval.

Submitting this input file to Spice results in the plot shown in Fig. 10.10. Both the input pulse to the amplifier and its output response are shown. Here we see that the positive-going portion of the output signal has a very different shape than the negative-going portion. Instead of a gradual rise in the positive-going signal, initially there is small jump in the output voltage of 2.2 volts, followed by the output being held constant at -2.8 V for 3.6 us, then rising linearly to +5 V in 18.2 us. Thus, the positive-going slew-rate is estimated at +0.55 V/us.

The negative-going response behaves more along the lines of what one expects, a steady decline from +5 V to -5 V. As a result, the negative-going slew-rate is found to be -0.39 V/us.

|

Fig. 10.8: Circuit arrangement for computing op amp positive- and negative-going slew-rate limits.

Fig. 10.10: Input and output transient voltage waveforms of the 741 op amp circuit connected in a unity-gain configuration. Both the positive-going and negative-going slew-rate limits of the op amp is evident from these results. |

The 741 Op-Amp

** Circuit Description **

* power supplies Vcc 25 0 DC +15V Vee 26 0 DC -15V

* slew-rate limiting set-up Vd 1 0 PWL ( 0,-5V 1ns,+5V 30000ns,+5V + 30001ns,-5V 1s,-5V ) Vshort 2 22 0

* 1st or input stage Q1 4 1 12 npn Q2 4 2 13 npn Q3 7 3 12 pnp Q4 8 3 13 pnp Q5 7 9 10 npn Q6 8 9 11 npn Q7 25 7 9 npn Q8 4 4 25 pnp Q9 3 4 25 pnp R1 10 26 1k R2 11 26 1k R3 9 26 50k

* 2nd stage Q13B 16 6 25 pnp 0.75 Q16 25 8 14 npn Q17 16 14 15 npn R8 15 26 100 R9 14 26 50k Cc 8 16 30p

* output or buffer stage Q13A 17 6 25 pnp 0.25 Q14 25 17 23 npn 3 Q18 17 18 19 npn Q19 17 17 18 npn Q20 26 19 21 pnp 3 Q23 26 16 19 pnp R6 22 23 27 R7 21 22 27 R10 18 19 40k

* short-circuit protection circuitry Q15 17 23 22 npn Q21 20 21 22 pnp Q22 8 20 26 npn Q24 20 20 26 npn R11 20 26 50k

* biasing stage Q10 3 5 24 npn Q11 5 5 26 npn Q12 6 6 25 pnp R4 24 26 5k R5 6 5 39k

* transistor model statements .model npn NPN ( Bf=200 Br=2.0 VAf=125V Is=10fA Tf=0.35ns + Rb=200 Rc=200 Re=2 Cje=1.0pF Vje=0.70V Mje=0.33 Cjc=0.3pF + Vjc=0.55V Mjc=0.5 Cjs=3.0pF Vjs=0.52V Mjs=0.5)

.model pnp PNP ( Bf=50 Br=4.0 VAf=50V Is=10fA Tf=30ns + Rb=300 Rc=100 Re=10 Cje=0.3pF Vje=0.55V Mje=0.5 Cjc=1.0pF + Vjc=0.55V Mjc=0.5 Cjs=3.0pF Vjs=0.52V Mjs=0.5)

** Analysis Requests ** .TRAN 0.1ns 100us

** Output Requests ** .PLOT TRAN V(1) V(22) .probe .end

Fig. 10.9: The Spice input deck for computing the positive- and negative-going slew-rate limit of the 741 op amp.

|

Noise Analysis of the 741 Op Amp

As our final analysis, we shall utilize the noise analysis capability of Spice to estimate both the output-referred and input-referred thermal noise power spectral density Sh(jw) of the 741 op amp circuit shown in Fig. 10.1. Analyzing the noise behavior of op amp circuits is a rather advanced topic and is not covered in the text by Sedra and Smith. It is included here because of its importance and to demonstrate yet another analysis capability of Spice.

Resistors and semiconductor devices generate various types of noise. Thermal noise is one important example of this noise, and the minimization of this noise component is an important consideration in the design of op amp circuits. The cause of thermal noise is the random movement of charge carriers in resistors or semiconductor devices. This movement, in turn, causes instantaneous voltage excursions to appear across the terminals of the device whose value, on average, is zero. In a circuit, these voltage variations also have an effect on the node voltages of the circuit. The total effect on any one particular node is simply the root-mean of the sum of the squares of each individual effect. The Noise Analysis capability of Spice performs exactly this computation in exactly this manner. In general, these noise fluctuations are functions of frequency and therefore are computed in conjunction with the .AC analysis of Spice. As a result, the noise level is reported in the output file in units of either V/ÖHz or A/ÖHz depending on its context.

The syntax of the Noise Analysis command is given in Table 10.3. The keyword .NOISE specifies that a noise analysis is to be performed on a given circuit over the frequency interval specified on the .AC command line. The next field output_voltage denotes a node voltage. The node(s) that this voltage appears across indicates the output port of the circuit. Spice will compute the effective noise voltage spectral density that appears at this port due to internal noise sources. Spice will not compute the effective output noise current spectral density associated with a short-circuit output. The subsequent field, indicated by source_name, specifies the name of an independent voltage or current source. The output noise voltage spectral density will be referred back to the port defined by this independent source as either an input-referred noise voltage or current spectral density depending on the input source type.

To access the noise information computed by Spice, one uses either a .PRINT or .PLOT command with reference to the information stored in the Spice variable ONOISE (output noise) or INOISE (equivalent input-referred noise).

Returning to the Spice input deck that we used to compute the frequency response of the op amp circuit, shown listed in Fig. 10.6, consider adding the following .NOISE command statement to the file, together with the statement specifying the output plot request:

|

.NOISE V(22) Vd .PLOT NOISE ONOISE INOISE |

Re-submitting the input file to Spice results in the output-referred and input-referred noise voltage spectral densities for the 741 op amp shown in Fig. 10.11. As a point of reference, we see that the output-referred noise voltage density at 1 kHz is 14.7 uV/ÖHz. Conversely, the output noise power spectral density can be referred to the input of the op amp at this same frequency to find 19.0 nV/ÖHz.

|

Table 10.3: The general syntax of the Noise Analysis command in Spice.

|

Fig. 10.11: Output and input-referred noise voltage spectral density of the 741 op amp circuit. The vertical axis is in units of V/ÖHz.

|

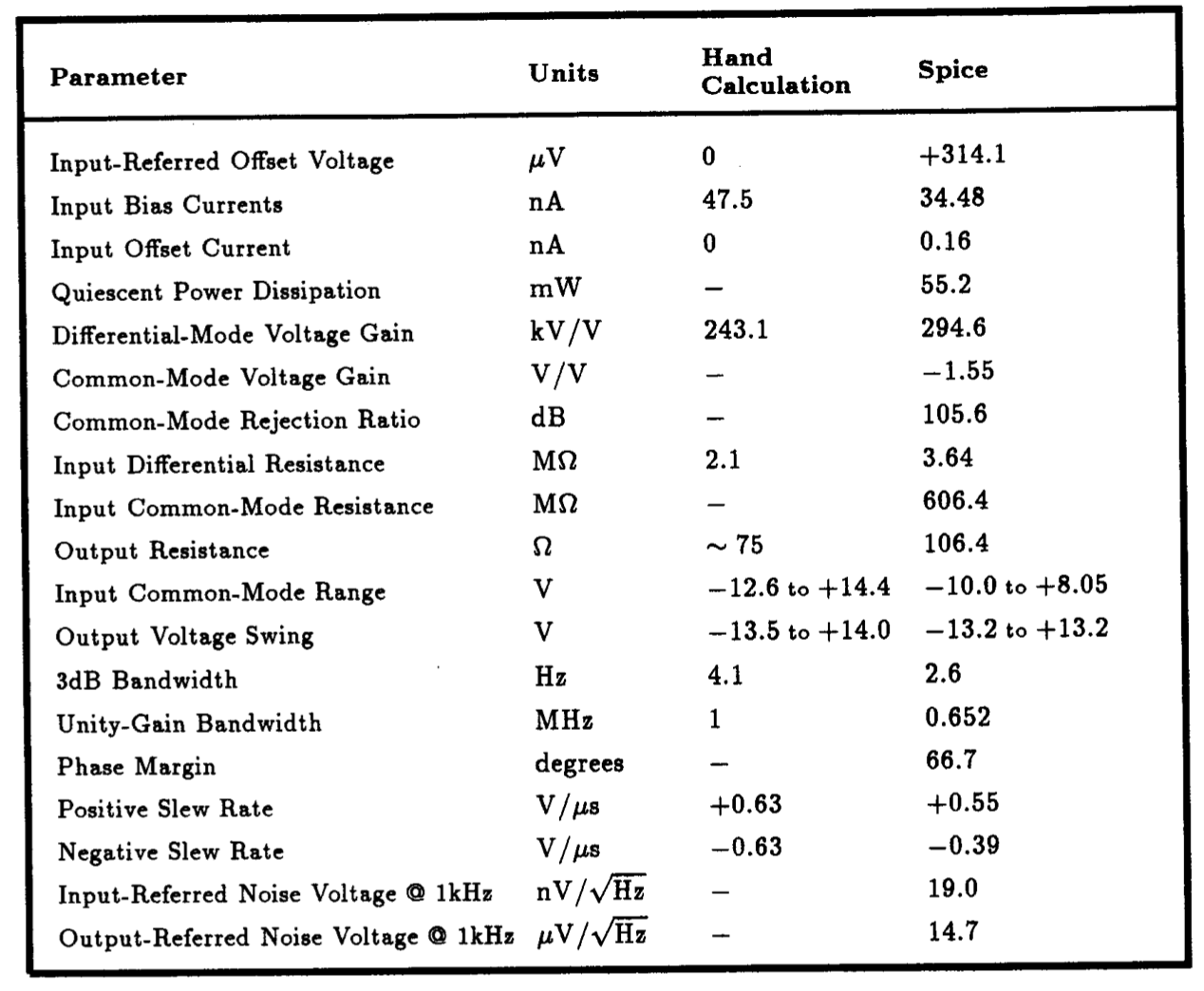

A Summary of the 741 Op Amp Characteristics

We summarize the results that we have obtained through the application of Spice to the 741 op amp in Table 10.4. Some of these results are also compared to those computed by hand in Sections 10.1-10.6 of Sedra and Smith. For the most part, the results obtained through hand analysis agree quite well with those computed with Spice. This is especially true for the parameters obtained through the small-signal analysis. The same cannot be said for many of the op amp's large-signal DC characteristics. We attribute this to the fact that the large-signal DC analysis performed by Sedra and Smith neglected the effect of transistor Early voltage, unlike that performed during the small-signal analysis. Of course, one could improve the accuracy of the hand analysis by including the effect of transistor Early voltage in the large-signal calculations; however, the additional complexity is probably not commensurate with the additional accuracy gained, especially when one could go directly to Spice.

|

Table 10.4: A comparison of the results of the analysis of the 741 op amp circuit shown in Fig. 10.1 by hand (Sedra and Smith) and Spice.

|

10.2 A CMOS Op Amp

In Fig. 10.12 we show a two-stage CMOS op amp circuit with the device geometries seen listed in Table 10.5. The input differential stage of this amplifier was previously analyzed in Section 6.4 of this text for its large-signal differential-mode and common-mode transfer characteristics, among other things. Here an additional gain stage has been added in order to increase the gain of the amplifier, and a compensation network is included to maintain stability when the op amp is connected in a negative feedback loop. In Example 10.2 of Sedra and Smith this amplifier stage was analyzed by hand with rather simple transistor models where it was found to have a DC differential gain of +3125 V/V, an input common-mode range varying between -4.5 V to +3.0 V, and an output voltage swing ranging between -4.5 V and +4.4 V.

In the following we shall recalculate the above parameters of the CMOS amplifier with Spice using more realistic transistor models. In particular, we shall consider that each MOSFET is modeled after the transistors found in the 5-micron CMOS process at Bell Northern Research (BNR). We shall then compare these results with those predicted by the simple formulae presented in Sedra and Smith in Example 10.2 of their text using the DC operating point information provided by Spice.

The Spice description of the CMOS amplifier is shown in Fig. 10.13. The differential input is driven by the multiple source arrangement shown in Fig. 10.3. A level 2 MOSFET model of each transistor type is provided with a lengthy list of device parameters. These were obtained through extensive measurements on transistors fabricated through the 5 um CMOS process at BNR. The first analysis requested is a DC sweep of the input differential voltage Vd between the two supply limits with the input common-mode level VCM set to 0 V.

|

Fig. 10.12: A two-stage CMOS op amp circuit with p-channel input transistors.

Table 10.5: Transistor geometries for the CMOS op amp circuit shown in Fig. 10.12.

|

Example 10.2: A CMOS Operational Amplifier (5um CMOS Models)

** Circuit Description ** * power supplies Vdd 4 0 DC +5V Vss 5 0 DC -5V * differential-mode signal level Vd 101 0 DC 0V Rd 101 0 1 EV+ 2 100 101 0 +0.5 EV- 1 100 101 0 -0.5 * common-mode signal level Vcm 100 0 DC 0V * front-end stage M1 7 1 6 4 pmos_transistor L=8u W=120u M2 8 2 6 4 pmos_transistor L=8u W=120u M3 7 7 5 5 nmos_transistor L=10u W=50u M4 8 7 5 5 nmos_transistor L=10u W=50u M5 6 9 4 4 pmos_transistor L=10u W=150u * 2nd gain stage M6 3 8 5 5 nmos_transistor L=10u W=100u M7 3 9 4 4 pmos_transistor L=10u W=150u * current source biasing stage M8 9 9 4 4 pmos_transistor L=10u W=150u Iref 9 5 25uA * compensation network Cc 8 10 10pF R 10 3 10k * 5um BNR CMOS transistor model statements .MODEL nmos_transistor nmos ( level=2 vto=1 nsub=1e16 tox=8.5e-8 uo=750 + cgso=4e-10 cgdo=4e-10 cgbo=2e-10 uexp=0.14 ucrit=5e4 utra=0 vmax=5e4 rsh=15 + cj=4e-4 mj=2 pb=0.7 cjsw=8e-10 mjsw=2 js=1e-6 xj=1u ld=0.7u ) .MODEL pmos_transistor pmos ( level=2 vto=-1 nsub=2e15 tox=8.5e-8 uo=250 + cgso=4e-10 cgdo=4e-10 cgbo=2e-10 uexp=0.03 ucrit=1e4 utra=0 vmax=3e4 rsh=75 + cj=1.8e-4 mj=2 pb=0.7 cjsw=6e-10 mjsw=2 js=1e-6 xj=0.9u ld=0.6u ) ** Analysis Requests ** .DC Vd -4mV +4mV 100uV ** Output Requests ** .PLOT DC V(3) .probe .end

Fig. 10.13: The Spice input file describing the CMOS amplifier shown in Fig. 10.12. A Level 2 MOSFET model of each type of transistor is given. |

|

Fig. 10.14: The large-signal differential-input transfer characteristics of the CMOS op amp circuit shown in Fig. 10.12. The input common-mode voltage level is set to zero volts.

|

Fig. 10.15: The large-signal common-mode DC transfer characteristics of the CMOS op amp circuit shown in Fig. 10.12. An input differential offset voltage of +220.0 uV is applied to prevent premature saturation.

|

The results of this DC sweep are shown plotted in Fig. 10.14. We see here that the linear region of the amplifier extends between the input voltage levels of -1.24 mV and +1.71 mV. Correspondingly, this gives rise to a maximum output voltage swing ranging between -4.40 V and +4.54 V. Thus, the small-signal differential gain can be estimated to be in the neighborhood of +3.031 kV/V. Also, we see that the input-referred offset voltage is approximately -220.0 uV.

Following this, we have performed a DC sweep of the input common-mode level with the differential input to the amplifier offset by +220.0 uV. To accomplish this, we replaced the DC sweep command given in Fig. 10.13 by the following one:

.DC Vcm -5V +5V 0.1V.

and modified the input differential voltage statement Vd according to:

Vd 101 0 DC +220.0uV.

The results of this analysis are displayed in Fig. 10.15. As is evident, the input common-mode range extends from the lower limit of the power supply VSS to +3.1 V. We can further add commands .TF and .OP into the Spice deck and obtain the small-signal DC gain of the circuit and any relevant DC operating point information. These two new commands would appear in the Spice deck as follows:

|

.OP .TF V(3) Vd. |

One would then find in the output file the following information:

|

**** SMALL SIGNAL BIAS SOLUTION TEMPERATURE = 27.000 DEG C ******************************************************************************

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1)-110.0E-06 ( 2) 110.0E-06 ( 3) .0125 ( 4) 5.0000 ( 5) -5.0000 ( 6) 1.8828 ( 7) -3.5404 ( 8) -3.5516 ( 9) 3.4242 ( 10) .0125 ( 100) 0.0000 ( 101) 220.0E-06

VOLTAGE SOURCE CURRENTS NAME CURRENT

Vdd -8.061E-05 Vss 8.061E-05 Vd -2.200E-04 Vcm 0.000E+00

TOTAL POWER DISSIPATION 8.06E-04 WATTS

NAME M1 M2 M3 M4 MODEL pmos_transistor pmos_transistor nmos_transistor nmos_transistor ID -1.34E-05 -1.34E-05 1.34E-05 1.34E-05 VGS -1.88E+00 -1.88E+00 1.46E+00 1.46E+00 VDS -5.42E+00 -5.43E+00 1.46E+00 1.45E+00 VBS 3.12E+00 3.12E+00 0.00E+00 0.00E+00 VTH -1.51E+00 -1.51E+00 9.52E-01 9.52E-01 VDSAT -3.18E-01 -3.18E-01 2.83E-01 2.83E-01 GM 7.18E-05 7.18E-05 5.35E-05 5.34E-05 GDS 7.85E-07 7.84E-07 6.05E-07 6.07E-07 GMB 8.53E-06 8.53E-06 3.88E-05 3.88E-05

NAME M5 M6 M7 M8 MODEL pmos_transistor nmos_transistor pmos_transistor pmos_transistor ID -2.69E-05 2.87E-05 -2.87E-05 -2.50E-05 VGS -1.58E+00 1.45E+00 -1.58E+00 -1.58E+00 VDS -3.12E+00 5.01E+00 -4.99E+00 -1.58E+00 VBS 0.00E+00 0.00E+00 0.00E+00 0.00E+00 VTH -9.59E-01 9.38E-01 -9.54E-01 -9.64E-01 VDSAT -4.56E-01 2.87E-01 -4.61E-01 -4.51E-01 GM 8.64E-05 1.14E-04 9.19E-05 8.08E-05 GDS 1.09E-06 6.85E-07 9.36E-07 1.42E-06 GMB 2.63E-05 8.17E-05 2.77E-05 2.48E-05

**** SMALL-SIGNAL CHARACTERISTICS

V(3)/Vd = 3.603E+03

INPUT RESISTANCE AT Vd = 1.000E+00

OUTPUT RESISTANCE AT V(3) = 6.210E+05

|

Here we see that the small-signal DC gain of +3.603 kV/V has the same order of magnitude as our earlier estimate. We can check this value against the gain predicted by the formulae derived in Sedra and Smith; A0=gm1(ro2||ro4) x gm6(ro6||ro7). Substituting the appropriate values from the above Spice generated small-signal data we see that A0=+3.630 kV/V, which agrees quite closely with the value predicted by the .TF command of Spice.

We can also make use of the above DC and small-signal information to estimate the input CMR of this amplifier and its output voltage swing. The lower limit of the input CMR is determined by M1 leaving the saturation region. This occurs when the voltage at the gate of M1 drops below the voltage at its drain (V(7)=-3.5404 V) by a single threshold level. From the above Spice generated data, we see that the threshold voltage of M1 is -1.51 V. We can then compute the lower limit of the input CMR to be -5.1 V. This limit seems to extend beyond VSS of -5 V, unlike that calculated by hand where it was found that the lower CMR limit is -4.5 V. The reason for the difference is that in the hand calculation a threshold voltage of -1 V for M1 was assumed neglecting its dependence on the source-substrate back-bias voltage (the body effect). If the hand calculation used the actual threshold voltage of M1 at -1.51 V, we would obtain the exact same lower limit to the CMR found through Spice.

The upper limit of the input CMR is determined by M5 leaving the saturation region. This occurs when the drain of M5 rises one threshold voltage above its gate voltage of +3.4242 V. The threshold voltage of M5 is -0.959 V. Hence, M1 leaves saturation when its drain voltage exceeds +4.38 V. To relate this voltage to the input of the amplifier, we simply subtract off the gate-source voltage of either M1 or M2. The result is the upper CMR limit of (4.38 V - 1.88 V) or +2.5 V. This is somewhat lower than that predicted by hand analysis at +3 V. It is also lower than that seen from the plot of the output voltage of the amplifier as a function of the input common-mode voltage shown in Fig. 10.15. There are two reasons for the discrepancy. The first is again due to the fact that the transistor body effect has been neglected. In addition, the current flowing through both M1 and M2 is somewhat reduced because of the dependence of the drain current of M5 on its drain voltage. This, in turn, decreases the gate-source voltage of M1 and M2. Thus, a larger input common-mode voltage can appear at the input terminals of the amplifier before any internal saturation occurs.

Following similar reasoning, the maximum range of the output voltage is one threshold voltage above the gate voltage of M7. Thus, it is simply (3.42 V + 0.954 V) or +4.37 V. Likewise, the minimum output voltage is one threshold voltage below the gate voltage of M6 and is therefore -4.49 V. These results seem to be reasonably close to the results that are visible from Fig. 10.14 using Probe (i.e., -4.40 V and +4.54 V) and those computed by hand (i.e., -4.5 V and +4.4 V).

|

(a)

|

(b)

|

|

Fig. 10.16: Folded-Cascoded Op Amp: (a) CMOS implementation (b) BiCMOS implementation.

|

|

|

Table 10.6: Transistor geometries for the CMOS op amp circuit shown in Fig. 10.16(a).

|

Table 10.7: DC drain and collector currents of the CMOS and BiCMOS circuits shown in Fig. 10.16(b) as computed by hand analysis.

|

10.3 Two Different Technology Versions of A Folded-Cascode Op Amp

In Fig. 10.16 we display two different versions of a folded-cascode op amp circuit; one realized using CMOS technology and the other using a combination of CMOS and Bipolar technology called BiCMOS. The dimensions of the various MOSFETs of the two circuits are provided in Table 10.16; the bipolar transistors are assumed all equal in size, except Q6 and Q7 which are three times the size of the other bipolar transistors.

In the following we shall compare the frequency response behavior of these two op amp circuits assuming that the MOSFETs are modeled with the complex BNR 5-micron CMOS models used in the previous section and the bipolar transistors are modeled using the complex set of parameters listed in Table 10.1. But before we begin this, we shall first compute the frequency response behavior of the two amplifiers by hand in order to obtain some sense of expected amplifier behavior. We shall assume that a simplified representation of the NMOS transistors are characterized by: Vt=1 V, unCOX=20 uA/V2 and =0.04 V-1; similarly, for the PMOS transistors: $Vt=-1 V, upCOX = 10 uA/V2 and l=0.04 V-1. A simplified model of the npn transistors of the BiCMOS circuit consists of IS=10 fA, b=200$ and VA=125 V.

According to the small-signal analysis performed by Sedra and Smith in Section 10.8 for a folded-cascode op amp, the voltage gain of either circuit is given by

(10.1)

![]()

where Ro is the output resistance of the op amp, given by

(10.2)

![]()

Moreover, the dominant pole of the amplifier is located at frequency

(10.3)

![]()

and the corresponding unity-gain frequency is

(10.4)

![]()

Performing a DC hand analysis on the folded-cascoded CMOS amplifier shown in Fig. 10.16(a) with the above mentioned MOSFET device and geometry parameters, we obtain their corresponding drain currents listed in Table 10.7. To simplify the analysis, we have neglected the effect of channel-length modulation. This analysis is rather straightforward owing to the fact that the reference current Iref is simply mirrored into the other branches of the op amp.

Repeating the same DC analysis for the BiCMOS amplifier shown in Fig. 10.16(b) while neglecting the base currents of the bipolar transistors, one obtains exactly the same drain currents for each MOSFET as was found in the CMOS amplifier. The collector current of each npn transistor is equal to the drain current of the MOSFET that it replaces. Even though a MOSFET is replaced by a bipolar transistor, the same mirroring action is used in each circuit (i.e., the same current gains).

Knowing the device operating currents, we can compute the small-signal parameters of the devices of interest, and thus, calculate expected frequency response behavior of the op amp. Below we list the transconductance and output resistance of the appropriate transistors of the CMOS and BiCMOS op amps. These can then be used to compute small-signal parameters $A_0$, Ro, fD and ft, as mentioned above.

|

|

Substituting the above small-signal parameters into Eqns. (10.1) - (10.4), we obtain the following small-signal frequency response data for the two op amps:

|

|

As is evident from this table of values, the BiCMOS op amp has a larger low frequency gain but a lower bandwidth than the corresponding CMOS version. Interestingly enough, both op amps have identical unity-gain bandwidths.

To investigate realistic op amp frequency response behavior, we make use of the two Spice decks listed in Figs. 10.17 and 10.18 where the transistors are modeled as mentioned earlier. A DC sweep command of the input differential voltage is performed first in order to locate the high-gain linear region of the amplifier. The common-mode input voltage level will be set at 0 V during this voltage sweep.

|

Fig. 10.16: (a) CMOS Folded-Cascoded Op Amp (duplicate) |

A Folded-Cascode CMOS Op-Amp

** Circuit Description ** * power supplies Vdd 4 0 DC +5V Vss 5 0 DC -5V * differential-mode signal level Vd 101 0 DC 0V AC 1V Rd 101 0 1 EV+ 1 100 101 0 +0.5 EV- 2 100 101 0 -0.5 * common-mode signal level Vcm 100 0 DC 0V * differential-pair steering control M1 8 1 3 4 pmos_transistor L=10u W=500u M2 9 2 3 4 pmos_transistor L=10u W=500u M5 3 14 4 4 pmos_transistor L=6u W=120u * cascode stage M3 13 12 4 4 pmos_transistor L=6u W=60u M4 12 12 4 4 pmos_transistor L=6u W=60u M3c 11 11 13 4 pmos_transistor L=6u W=60u M4c 10 11 12 4 pmos_transistor L=6u W=60u

M1c 11 7 8 5 nmos_transistor L=6u W=60u M2c 10 7 9 5 nmos_transistor L=6u W=60u M6 8 6 5 5 nmos_transistor L=6u W=60u M7 9 6 5 5 nmos_transistor L=6u W=60u * biasing stage M8 7 7 6 5 nmos_transistor L=6u W=60u M9 6 6 5 5 nmos_transistor L=6u W=20u M10 7 14 4 4 pmos_transistor L=6u W=30u M11 14 14 4 4 pmos_transistor L=6u W=30u Iref 14 5 5uA * load capacitance Cl 10 0 10pF * transistor model statements * 5u BNR CMOS transistor model statements .MODEL nmos_transistor nmos ( level=2 vto=1 nsub=1e16 tox=8.5e-8 uo=750 + cgso=4e-10 cgdo=4e-10 cgbo=2e-10 uexp=0.14 ucrit=5e4 utra=0 vmax=5e4 rsh=15 + cj=4e-4 mj=2 pb=0.7 cjsw=8e-10 mjsw=2 js=1e-6 xj=1u ld=0.7u ) .MODEL pmos_transistor pmos ( level=2 vto=-1 nsub=2e15 tox=8.5e-8 uo=250 + cgso=4e-10 cgdo=4e-10 cgbo=2e-10 uexp=0.03 ucrit=1e4 utra=0 vmax=3e4 rsh=75 + cj=1.8e-4 mj=2 pb=0.7 cjsw=6e-10 mjsw=2 js=1e-6 xj=0.9u ld=0.6u ) ** Analysis Requests ** .DC Vd -10mV +10mV 100uV ** Output Requests ** .PLOT DC V(10) .probe .end

Fig. 10.17: The Spice input file describing the folded-cascode CMOS amplifier.

|

|

Fig. 10.16: (b) Folded-Cascoded BiCMOS Op Amp. (duplicate) |

A Folded-Cascode BiCMOS Op-Amp

** Circuit Description ** * power supplies Vdd 4 0 DC +5V Vss 5 0 DC -5V * differential-mode signal level Vd 101 0 DC 0V Rd 101 0 1 EV+ 1 100 101 0 +0.5 EV- 2 100 101 0 -0.5 * common-mode signal level Vcm 100 0 DC 0V * differential-pair steering control M1 8 1 3 4 pmos_transistor L=10u W=500u M2 9 2 3 4 pmos_transistor L=10u W=500u M5 3 14 4 4 pmos_transistor L=6u W=120u * cascode stage M3 13 12 4 4 pmos_transistor L=6u W=60u M4 12 12 4 4 pmos_transistor L=6u W=60u M3c 11 11 13 4 pmos_transistor L=6u W=60u M4c 10 11 12 4 pmos_transistor L=6u W=60u

Q1c 11 7 8 5 npn_transistor Q2c 10 7 9 5 npn_transistor Q6 8 6 5 5 npn_transistor 3 Q7 9 6 5 5 npn_transistor 3 * biasing stage Q8 7 7 6 5 npn_transistor Q9 6 6 5 5 npn_transistor M10 7 14 4 4 pmos_transistor L=6u W=30u M11 14 14 4 4 pmos_transistor L=6u W=30u Iref 14 5 5uA * load capacitance Cl 10 0 10pF * transistor model statements * Bipolar transistor model statements .model npn_transistor NPN ( Bf=200 Br=2.0 VAf=125V Is=10fA Tf=0.35ns + Rb=200 Rc=200 Re=2 Cje=1.0pF Vje=0.70V Mje=0.33 Cjc=0.3pF Vjc=0.55V + Mjc=0.5 Cjs=3.0pF Vjs=0.52V Mjs=0.5 ) * 5u BNR CMOS transistor model statements .MODEL pmos_transistor pmos ( level=2 vto=-1 nsub=2e15 tox=8.5e-8 uo=250 + cgso=4e-10 cgdo=4e-10 cgbo=2e-10 uexp=0.03 ucrit=1e4 utra=0 vmax=3e4 rsh=75 + cj=1.8e-4 mj=2 pb=0.7 cjsw=6e-10 mjsw=2 js=1e-6 xj=0.9u ld=0.6u ) ** Analysis Requests ** .DC Vd -10mV +10mV 100uV ** Output Requests ** .PLOT DC V(10) .probe .end

Fig. 10.18: The Spice input file describing the folded-cascode BiCMOS amplifier. |

|

Fig. 10.19: The large-signal differential transfer characteristics of the CMOS and BiCMOS amplifiers shown in Fig. 10.16.

|

Fig. 10.20: A comparison of magnitude and phase response of the CMOS and BiCMOS amplifiers shown in Fig. 10.16. |

On completion of Spice, the large-signal differential characteristics of the CMOS and BiCMOS amplifiers are shown plotted in Fig. 10.19. As is evident, they have similar DC gains (i.e., slope of the linear region), with the BiCMOS circuit having a slightly larger gain. From these results we have determined with the aid of Probe that the DC offset of the CMOS and BiCMOS amplifiers are -857.1 uV and -500 uV, respectively. Also apparent, the output voltage swing of the BiCMOS amplifier is about one volt larger than its CMOS counterpart.

Offsetting the input to the two amplifiers with the appropriate DC voltage so that each amplifier is biased inside its linear region, we can compute the frequency response of each amplifier. This is accomplished by altering the input signal source statement in the Spice deck for the CMOS amplifier according to

Vd 101 0 DC -857.1uV AC 1V

and, likewise, for the BiCMOS amplifier with

Vd 101 0 DC -500.0uV AC 1V,

and adding the following AC analysis command in each input file

.AC DEC 10 1Hz 100MegHz,

we can then submit the revised Spice decks for analysis. The magnitude and phase behavior of the two amplifiers, as computed by Spice, are shown together in Fig. 10.20. Using Probe we were able to extract the following frequency response information from these results:

Examining the above results, we see that the BiCMOS amplifier has a slightly larger low-frequency gain but a lower 3 dB bandwidth than the corresponding CMOS amplifier. This manifest itself into the CMOS amplifier having a larger unity-gain bandwidth product than the BiCMOS amplifier. In comparison with the results computed previously by hand, we find that the predicted DC gain and 3 dB bandwidth for the two amplifiers are quite different. The reason for the discrepancy can be traced back to the rather crude estimates of the small-signal model parameters used to compute them. There are two reasons for this: the simplified model parameters for the MOSFETs used in the hand calculations are not truly representative of actual transistor behavior, and secondly, the effect of transistor Early voltage and body-effect were neglected when the transistor bias levels were being computed. Using the small-signal parameters generated by Spice through the .OP command, hand analysis using Eqns. (10.1)-(10.4) will generate results similar to those computed by Spice. We leave this for the reader to confirm using Spice.

The final point that we want to discuss here is the location of the second or nondominant pole of each amplifier. According to the frequency response results shown in Fig. 10.20 the CMOS amplifier has a nondominant pole at 36 MHz. Whereas, the BiCMOS amplifier has its nondominant pole located at a much lower frequency of only 4.5 MHz. This result is rather contrary to what one would expect when a MOSFET is replaced by a corresponding bipolar transistor biased at the same current level. Since, after all, a bipolar transistor has a higher transconductance than a corresponding MOSFET when biased at the same current level. However, this is not the entire story because the location of the nondominant pole is also determined by the parasitic capacitance associated with the transistor. As it turns out, in this particular case, the bipolar transistors used to replace the NMOS transistors have associated with it a much larger parasitic capacitance (this can be confirmed by viewing the small-signal model data generated by Spice for each transistor). Thus, what signal strength is gained from the increased transconductance is lost in the frequency domain to the added parasitic capacitance of the bipolar transistor. This is not necessarily what would happen in an actual design as the models for the MOSFETs and npn transistors used in this example were simply contrived and do not represent an actual BiCMOS technology.

10.4 Data Converters

Analog-to-digital (A/D) and digital-to-analog (D/A) converter circuits are important components of electronic systems. In the following we shall simulate the ideal behavior of a D/A and an A/D converter using Spice. More specifically, we shall simulate the operation of the conversion of a 4-bit digital word into a corresponding analog signal using a 4-bit R-2R ladder D/A converter circuit. Secondly, we shall also observe the conversion of an analog signal into a 3-bit digital signal using a flash converter. Our objective here is to investigate basic circuit operation as opposed to observing nonideal behavior.

R-2R Ladder D/A Converter

Figure 10.21 displays the circuit schematic of a 4-bit D/A converter utilizing an R-2R ladder network. The double throw switches are assumed ideal and are controlled by the appropriate voltage source whose level represents a single bit of a 4-bit digital number. It is precisely this digital number that is to be converted into an equivalent analog signal. The op amp is assumed pseudo-ideal and represented by the high-gain VCVS shown in Fig. 10.21(b). A Spice description of this circuit is shown listed in Fig. 10.22. Four digital signal generators are provided, generating the entire sequence of digital words possible with 4-bits over an 8 ms interval. A low logic level is represented by 0 V and a high logic level by +5 V.

Of special interest, and not seen by the reader until now, is the PSpice element statement used to represent a voltage-controlled switch. This element is not available in all versions of Spice, but greatly simplifies circuit modeling, and thus, is employed here to represent a single-pole single-throw switch[2]. The general syntax of the PSpice voltage-controlled switch statement is shown in Fig. 10.23. Two statements are necessary to describe a voltage-controlled switch to PSpice: a statement beginning with the letter S (for switch) specifying the connections made to the rest of the network and the name of the model used to characterize the switch. Another statement, cross-referenced to this element statement, contains a list of four parameters that describe the terminal behavior of the switch. These are: Von, the control voltage level required to turn on the switch; Voff, the voltage level that turns off the switch; and Ron and Roff, the on- and off-resistance of the switch, respectively.

|

(a)

(b)

Fig. 10.21: (a) A D/A converter utilizing an R-2R ladder network (b) op amp equivalent circuit.

|

R-2R Ladder D/A Converter

** Circuit Description **

* op-amp subcircuit .subckt ideal_opamp 1 2 3 * connections: | | | * output | | * +ve input | * -ve input Iopen1 2 0 0A Iopen2 3 0 0A Ecomp 1 0 2 3 1e6 .ends ideal_opamp

** Main Circuit ** * input digital signals Vd1 14 0 PULSE (5 0 0 1ns 1ns 0.5ms 1ms) Vd2 13 0 PULSE (5 0 0 1ns 1ns 1ms 2ms) Vd3 12 0 PULSE (5 0 0 1ns 1ns 2ms 4ms) Vd4 11 0 PULSE (5 0 0 1ns 1ns 4ms 8ms) * reference voltage Vref 7 0 DC 1V * R-2R ladder network R1 7 8 10k R2 8 9 10k R3 9 10 10k R4 10 0 20k R5 6 7 20k R6 5 8 20k R7 4 9 20k R8 3 10 20k * switches S1 3 2 14 0 switch_model S1c 3 0 14 0 complementary_switch_model S2 4 2 13 0 switch_model S2c 4 0 13 0 complementary_switch_model S3 5 2 12 0 switch_model S3c 5 0 12 0 complementary_switch_model S4 6 2 11 0 switch_model S4c 6 0 11 0 complementary_switch_model * current-to-voltage converter Rf 1 2 10k Xopamp 1 0 2 ideal_opamp * switch model .model switch_model vswitch (Ron=1 Roff=1e6 Von=5V Voff=0V) .model complementary_switch_model vswitch (Ron=1 Roff=1e6 Von=0V Voff=5V) ** Analysis Requests ** .TRAN 500us 8ms 0 500us ** Output Requests ** .PRINT TRAN V(1) V(11) V(12) V(13) V(14) .probe .end

Fig. 10.22: The PSpice input file for analyzing the D/A converter shown in Fig. 10.21.

|

|

Fig. 10.23: PSpice element and model description of a voltage-controlled switch. This element is not available in some versions of Spice but can be realized in Spice using a nonlinear voltage-controlled current source; see footnote on page xx.

|

In the PSpice description of the D/A converter seen listed in Fig. 10.22, the double-throw switch is represented by two complementary switches driven by the same digital control signal. The switches are complementary in the sense of their state of conduction. That is, one switch is conducting while the other is blocking.

The results of the transient analysis are shown in Fig. 10.24. The top graph displays the sequence of digital signals applied as input to the D/A converter and the bottom graph displays the corresponding analog output signal. The glitches seen superimposed on the analog output signal are due to the very short interval when all the switches disconnect from the op amp negative input terminal on their way to their next position.

3-Bit A/D Flash Converter

In Fig. 10.25 we display a 3-bit A/D flash converter circuit. Seven comparators are required for 3-bit accuracy. A 10 kW resistor string is used to realize the reference voltages for the various comparators. An input voltage signal Vi is applied to the positive input terminal of each comparator, and if the input signal is larger than the reference voltage applied to the negative input terminal, the output of the comparator goes into its high logic state, otherwise it remains in its low state.

In the following we shall compute the output state of each comparator as a function of the input voltage level using Spice. We shall model the terminal characteristics of each comparator using the equivalent circuit shown in part (b) of Fig. 10.25. The front-end portion of the comparator is modeled as a high-gain amplifier with a VCVS. The output of the amplifier is maintained within the limits of the two power supplies by clamping the output voltage to one of the supply levels using the diode and DC voltage source limiter. The diodes will be assumed ideal, and made nearly so, by setting n small in the diode model statement (i.e., n=0.01).

|

(a)

|

(b)

|

|

|

Fig. 10.24: Signal waveforms of the D/A converter shown in Fig. 10.21: (a) switch control signals (b) analog output voltage signal as a function of time.

|

|

|

The Spice file describing this circuit is shown listed in Fig. 10.26. Here we are requesting a DC sweep of the input voltage beginning at the lower power supply limit of -5 V and ending at the +5 V power supply level. In this way, we should be able to exercise all possible states of the A/D converter.

On completion of Spice, we have plotted the output voltage of each comparator as a function of the input voltage level, as shown in Fig. 10.27. Clearly, for an input voltage level between -5 V and -3.75 V all comparator outputs are logically low. Subsequently, with the input increased to some level somewhere between -3.75 V and -2.5 V, comparator C7 goes logically high with all other comparators remaining in the logic low state. Continuing, for the next input voltage interval between -2.5 V and -1.25 V, we see that comparator C6 has now also gone into its high state. As we further increase the input voltage level, C5 will be the next one that goes into its high state. This will be followed by C4, C3, etc.., until all comparator outputs are logically high when the input level exceeds +3.75 V. Since the combined output of this A/D has 8 possible states, it can be represented by a 3-bit binary number. This conversion would be performed by a digital circuit that would follow the A/D converter.

|

(a)

(b)

Fig. 10.25: (a) A 3-Bit A/D flash converter utilizing 7 comparator circuits. (b) equivalent circuit representation of the comparator circuit.

|

A 3-Bit A/D Flash Converter

** Circuit Description **

* comparator subcircuit .subckt comparator 1 2 3 * connections: | | | * output | | * +ve input | * -ve input Iopen1 2 0 0A Iopen2 3 0 0A Ecomp 6 0 2 3 1e6 Rout 6 1 10 V+sat 4 0 DC +5V V-sat 5 0 DC -5V D1 1 4 ideal_diode D2 5 1 ideal_diode .model ideal_diode D (Is=100pA n=0.01) .ends comparator

** Main Circuit **

* power supplies Vcc 1 0 DC +5V Vee 9 0 DC -5V * input signal source Vi 11 0 DC 0V * reference levels for comparators R1 1 2 10k R2 2 3 10K R3 3 4 10k R4 4 5 10k R5 5 6 10k R6 6 7 10k R7 7 8 10k R8 8 9 10k * comparators Xc1 10 11 2 comparator Rd1 10 0 1k Xc2 20 11 3 comparator Rd2 20 0 1k Xc3 30 11 4 comparator Rd3 30 0 1k Xc4 40 11 5 comparator Rd4 40 0 1k Xc5 50 11 6 comparator Rd5 50 0 1k Xc6 60 11 7 comparator Rd6 60 0 1k Xc7 70 11 8 comparator Rd7 70 0 1k ** Analysis Requests ** .DC Vi -5V +5V 100mV ** Output Requests ** .PLOT DC V(10) V(20) V(30) V(40) V(50) V(60) V(70) .probe .end

Fig. 10.26: The Spice input file for analyzing the A/D converter shown in Fig. 10.25.

|

|

|

(a)

|

(b)

|

|

|

Fig. 10.27: The output digital waveforms from the comparators of the A/D 3-bit flash converter shown in Fig. 10.25.

|

||

10.5 Spice Tips

· Inputs to differential amplifiers should consist of both a differential and a common-mode component. An interesting arrangement of several voltage sources was given in this chapter, illustrating how the differential and common-mode components can be independently adjusted.

· Performing a proper small-signal analysis on a high-gain amplifier circuit requires that the linear region of the amplifier be first located before any transfer function or frequency analysis is performed.

· The linear region of an op amp is located by first sweeping the input differential voltage vd between the limits of the power supplies with the common-mode voltage VCM equal to 0 V. This analysis is repeated with a reduced sweep range centered more closely around the high-gain linear region of the amplifier until a smooth transition through the high-gain linear region is achieved. Following this, one must check to see whether the input common-mode voltage of 0 V keeps the amplifier in its linear region.

· To quickly converge on the location of the high-gain region of an op amp, one can connect the op amp in a unity-gain configuration with the positive terminal of the op amp connected to ground and compute the input-referred offset voltage of the op amp VOS. Knowing this voltage, we can infer that the differential transfer characteristics of the op amp will cross the horizontal voltage axis (Vo=0 V) at -VOS. This is usually a valid point within the high-gain region of the op amp.

· Once the linear region of the amplifier is located, the correct DC conditions can be applied to the inputs of the amplifier to establish the proper bias point about which the small-signal analysis of Spice can be performed.

· The small-signal input resistance of an op amp is computed using Spice by applying a known AC voltage across the input terminals of the differential amplifier and computing the AC currents that flow into the amplifier terminals. In many practical amplifier situations, these currents will not be equal. So, instead, the average of these two currents is used in the input resistance calculation.

· The output thermal noise behavior of electronic circuits can be estimated using the noise analysis capability of Spice.

· A voltage-controlled switch can be modeled in PSpice using a special element and model statement for the switch. An equivalent realization of a voltage-controlled switch can be described to Spice using a nonlinear VCCS statement having the following form: Gswitch n+ n- poly(2) nc+ nc- n+ n- 0 0 0 0 1/Ron.

10.6 Bibliography

P.R. Gray and R.G Meyer, Analysis and Design of Analog Integrated Circuits, 2nd ed. New York: Wiley, 1984.}

10.7 Problems

10.1. Determine, with the aid of Spice, the differential-mode and common-mode voltage gain of the 741 op amp when the power supplies are reduced to ±5 V.

10.2. Assume that the IC process used to fabricate the 741 op amp circuit undergoes some variation that causes the Early voltage of each device to decrease by 30%, but all other parameters remain invariant. Making the appropriate changes to the Spice parameters listed in Table 10.1, recalculate the large and small-signal parameters of the 741 op amp seen listed in Table 10.4 and compare them to those listed in this table.

10.3. One way to eliminate the input-referred offset voltage of an op amp such as the 741 is to connect what is known as a nulling resistor between the emitters of Q5 and Q6 of the first stage of the op amp seen in Fig. 10.1. With the aid of Spice determine the value of this nulling resistor that will cause the input offset voltage to be reduced to a value less than 10 uV. Hint: Connect the op amp in a unity-gain configuration and adjust the value of the nulling resistor to eliminate the offset voltage.

10.4. Through a processing imperfection, the b of Q4 in Fig. 10.1 is reduced to 25 while the b of Q3 remains at its regular value of 50. Find the input offset voltage that this mismatch introduces using Spice.

10.5. For a 741 op amp employing ±7.5 V supplies, determine the maximum output voltage swing possible.

10.6. Determine the phase and gain margin of the 741 op amp when the compensation capacitor CC is reduced from 30 pF down to 20 pF. Will the amplifier be stable when it is connected in a unity-gain configuration? Use the device parameters provided in Table 10.1.

10.7. This problem involves investigating the short-circuit protection capability of the 741 op amp. Consider connecting the op amp in a unity-gain configuration with the output terminal connected directly to ground. With the input to the voltage follower connected to +5 V, compare the power dissipated by the output stage with and without the internal short-circuit protection circuitry in place.

10.8. In a particular design of the CMOS op amp of Fig. 10.12 the designer wishes to investigate the effects of increasing W/L ratio of both M1 and M2 by a factor of 4. Assuming that all other parameters are kept unchanged:

(a) Find the resulting change in (|VGS| - |Vt|) and in gm of M1 and M2.

(b) What change results in the voltage gain of the input stage? Also, how does this affect the overall voltage gain?

(c) What is the effect on the input offset voltage?

(d) If ft is to remain the same as before the change to M1 and M2, what is the new value of CC?

10.9. Consider a CMOS amplifier that is complementary to that in Fig. 10.12 in which each device is replaced by its complement of the same physical size with the supplies reversed. Use the overall conditions as specified in Section 10.2. For all devices have Spice compute ID and the small-signal parameters gm and ro. Compute the gain of the first and second stage, the overall amplifier voltage gain, the input common-mode range, and the output voltage range.

10.10. Using Spice determine the frequency response behavior of the CMOS folded-cascoded op amp shown in Fig. 10.16 for a load capacitance of 1 pF, 5 pF, 10 pF, 20 pF and 100 pF. How does the amplifiers phase margin vary?

10.11. The circuit in Fig. 10.21 can be used to multiply an analog signal by a digital one by feeding the analog signal to the Vref terminal. In this case the D/A converter is called a multiplying DAC or MDAC. Given an input sine-wave signal of 0.1sin(wt) volts, use the circuit of Fig. 10.21 together with an additional op amp to obtain vo = 10D x sin(wt) where D is the digital word given by

![]()

With the aid of Spice, compute the output transient voltage waveform of the DAC for the following values of D: (i) 0110 (ii) 1111, and (iii) 0000.

10.12. Repeat Problem 10.11 above, but this time, consider having the digital word D cycle through a digital pattern that resembles a symmetrical triangular waveform of 1/10-th the frequency of the input sinewave. Using the transient analysis command of Spice, plot the output voltage waveform from the MDAC.

10.13. Using Spice compute the input resistance seen by Vref in the circuit of Fig. 10.21 for all possible combinations of the switches.

10.14. With the aid of Spice, compare the transfer characteristics of the D/A converter shown in Fig. 10.21 with those obtained from an identical converter experiencing a +10% increase in the value of resistor R4.